Alveo U50でもVivadoを用いて独自HWを実装できることを知ったので,手始めにx86-U50間のDMAサンプルを動かしてみました.

その際に,困ったことやその解決策をおぼえがきとして残します.

環境

| OS | Ubuntu 20.04.6 LTS |

| Kernel | 5.15.0-69-generic |

| FPGA | Alveo U50 |

| Vitis_IDE | 2022.1 |

| XRT_Version | 2.14.354 |

| XRT_Branch | 2022.2 |

参考にしたサイト

ほとんどQiitaの記事通りに進めました.

Qiitaの記事との相違点

参考にした記事では,

[/axi_bram_ctrl_0/S_AXI]の[Master Base Address]を

[ 0x0000_0000_C000_0000 ]

[ 0x0000_0000_0000_0000 ] に変更していますが,今回試した手順では変更を加えていません.

元記事が,このようにしている意図は不明です.

他に,ドライバをロードする際に

modprobe xdma

ではうまくいかなかったので,gitのReadMeにあるプランB(testsの中にあるload_driver.shを実行する方法)でドライバを読みこませたところDMAのテストが正常に動作した.

Usageを引用しておく.

Usage:

https://github.com/Xilinx/dma_ip_drivers/blob/master/XDMA/linux-kernel/readme.txt

– Change directory to the driver directory.

cd xdma

– Compile and install the kernel module driver.

make install

– Change directory to the tools directory.

cd tools

– Compile the provided example test tools.

make

– Load the kernel module driver:

a. modprobe xdma

b. using the provided script.

cd tests

./load_driver.sh

– Run the provided test script to generate basic DMA traffic.

./run_test.sh

For more extensive memory mapped test:

assume the XDMA FGPA is at pci slot 0000:01:00.0

cd scripts_mm

./xdma_mm.sh 0000:01:00.0 | tee /tmp/xdma_mm.log

– Check driver Version number

modinfo xdma (or)

modinfo ../xdma/xdma.ko

エラー1:原因と対処法

Generate Bitstreamで以下のエラーが生じました.[DRC PPURQ-1] CATTRIP_PkgPin_driver_requirement: The HBM Catastrophic Over Temperature Output signal on the PACKAGE_PIN J18 (not placed) has no signal. It is required to have IOSTANDARD of LVCMOS18 and be driven by an OBUF with an active signal or GROUND. Failure to drive the pin correctly will require a card RMA.

原因は2つありました.

1つ目:制約ファイルを指定していないことで,(たしかHBM周辺につながる)J18ピンに値が入っていないぞというものでした.

これは,AMD(Xilinx)から提供されているXDCファイル(alveo-u50-xdc_20210505.zipを展開したもの)を制約ファイルとして指定します.(これだけでは解決しません.以下の2つ目の対処も行いました)

https://www.xilinx.com/products/boards-and-kits/alveo/u50.html#vivado

ここからボードファイルと,制約ファイル(XDC File)をダウンロードできます.

2つ目:

制約ファイルの251-3行目に以下の記述があります.

しかし,このままでは HBM_CATTRIP というポートが存在しない為エラーは解消しません.

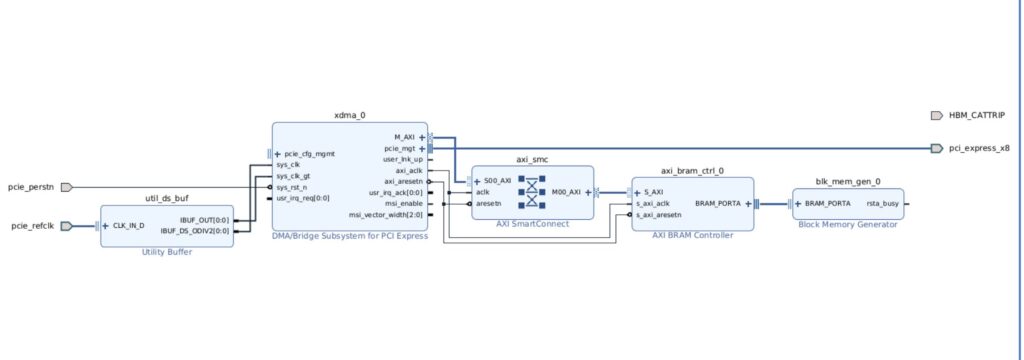

そのため,VivadoのBlock Designで”HBM_CATTRIP”というポートを作成することで解決します.

(かしこい解決策がありましたら教えてほしいです)

set_property PACKAGE_PIN J18 [get_ports "HBM_CATTRIP"] ;# Bank 68 VCCO - VCC1V8 - IO_L6N_T0U_N11_AD6N_68

set_property IOSTANDARD LVCMOS18 [get_ports "HBM_CATTRIP"] ;# Bank 68 VCCO - VCC1V8 - IO_L6N_T0U_N11_AD6N_68

set_property PULLDOWN TRUE [get_ports "HBM_CATTRIP"] ;# Bank 68 VCCO - VCC1V8 - IO_L6N_T0U_N11_AD6N_68

最終的なデザインは以下のようになります.

エラー2:原因と対処法

Open Hardware Manager から Open Target を押してもFPGAが開けず,Program Deviceが押せないエラーが生じました.

これは,単にドライバをインストールすれば解決します.

ドライバのインストールは,

[Vivado Install Dir.]/[IDE_Version]/data/xicom/cable_drivers/lin64/install_script/install_driver

というディレクトリに移動し

sudo ./install_drivers

を実行することでインストールできます.

このドライバは,Alveoに限らずZyboなどを使う際にも必要になります.

インストール後,再起動することでVivadoからFPGAを認識できます.

コメント

参考になりますーー