KR260 にはSFP+が実装されていて,10G通信ができる.

いままでなんとなくで使っていたIPについて調べてみる.

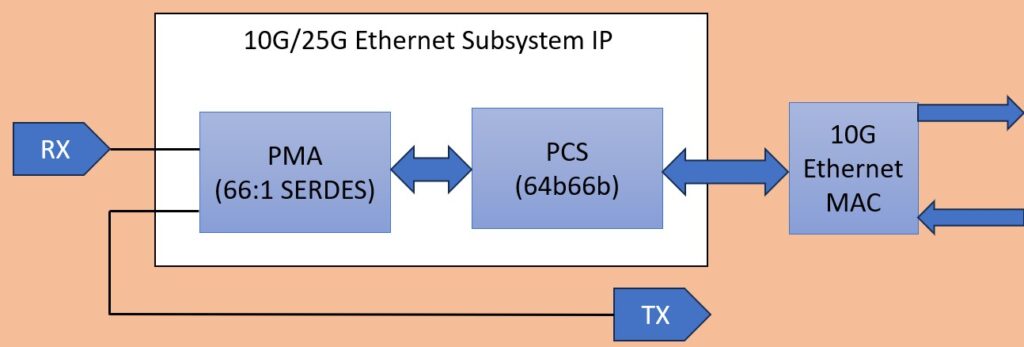

このIPには,PMA・PCS・MACが含まれているが,MACの機能を使うと有償のライセンスが必要になる.そのため,個人で利用する多くの場合はMAC IPを自作するか適当なものを拾ってくる必要がある.

このような,10G/25G Ethernet Subsystem IP でMACを利用しない場合に関しての情報をまとめる.

このような使い方をしている例としてFixstersさんの記事がありました.

https://proc-cpuinfo.fixstars.com/2020/05/alveo-u50-10g-ethernet

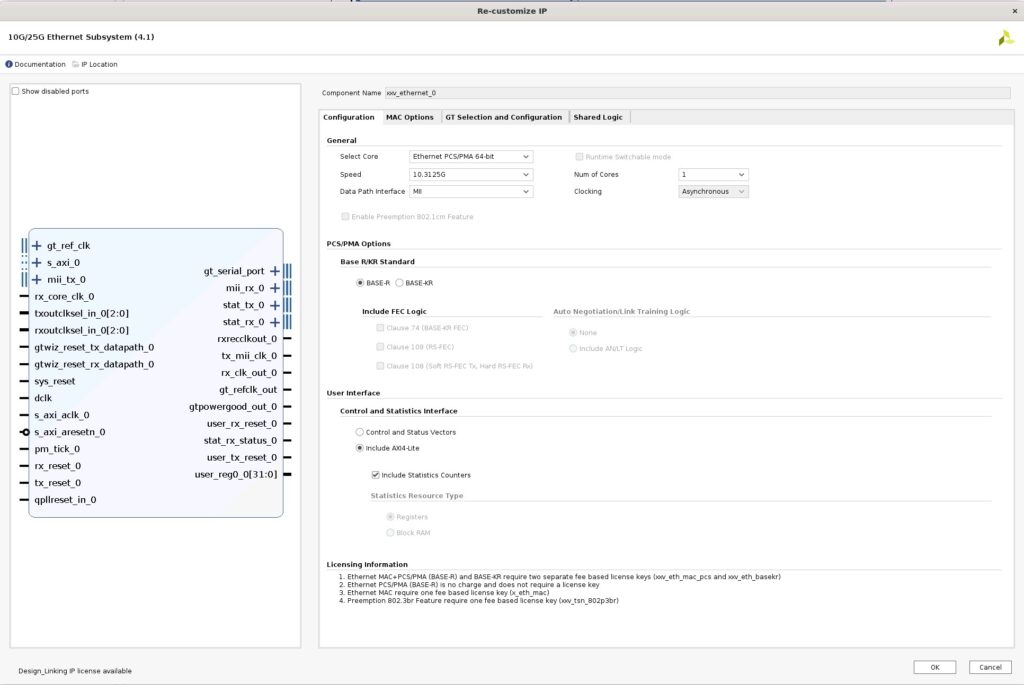

以下の様に設定した場合について調査したメモ.(Configurations以外のタブは全てデフォルトのまま.)

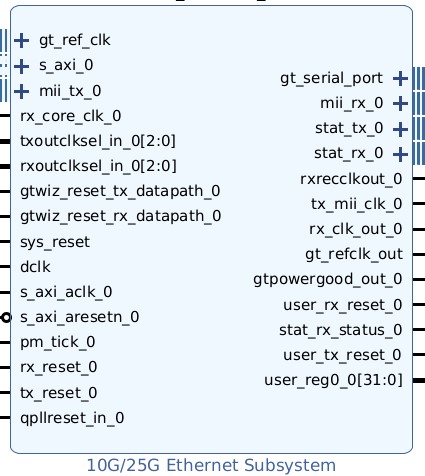

クロック

gt_ref_clk:GTYトランシーバの差動クロック

- gt_ref_clk_n : 差動クロック,KR260ではY5へ接続されているクロック(156.25MHz)を利用

- gt_ref_clk_p : 差動クロック,KR260ではY6へ接続されているクロック(156.25MHz)を利用

- tx_mii_clk:TX側のMIIバスで用いるクロックは,tx_mii_clkに同期させる必要あり.

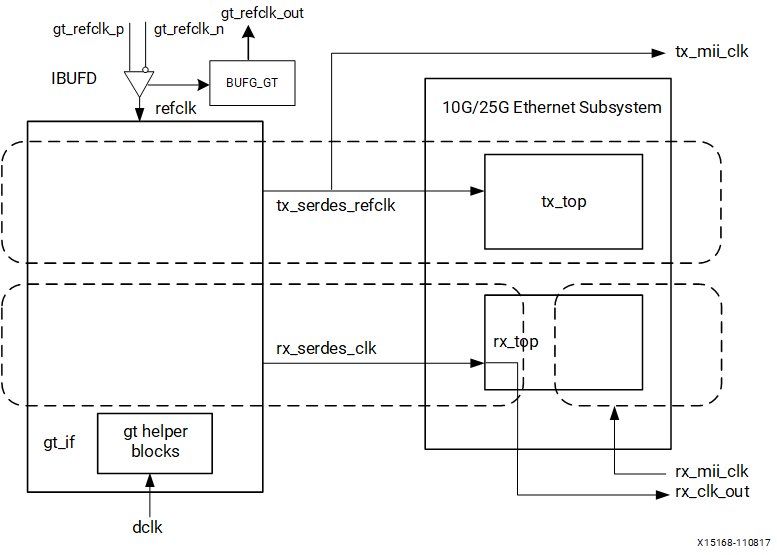

以下PG210の一部の日本語訳

”tx_mii_clk は出力信号であり,tx_serdes_refclk と同じクロックです.TX パス全体はこのクロックで駆動されます.このクロック出力に TX パスの MII バスを同期させる必要があります.すべての TX 制御およびステータス信号はこのクロックを基準にします.” - dclk:GT DRP (Dynamic Reconfiguration Port)用のクロック.DRPはAXI4-Liteで駆動する為,AXI4-Liteのマスタ側のクロックソースと接続.

- gt_refclk_out:差動入力された gt_ref_clk を バッファ越しに出力.

- rx_serdes_clk:CDR(Clock Data Recovery)によるクロック生成から復元されたクロック.子のクロックは受信データと同期している.

- rx_clk_out:rx_serdes_clkに等しい.

- rxrecclkout:GTレシーバの受信側で再生されたクロック出力

rx_core_clk

rx_core_clk:以下の通り.

以下PG210の一部の日本語訳

”rx_core_clk 信号は RX の AXI4-Streamインターフェースのクロックに使用される.FIFO が含まれない場合,rx_clk_out で駆動する必要があります.FIFO が含まれる場合,rx_core_clk は tx_clk_out,rx_clk_out,または同じ周波数の非同期クロックで駆動できる.”

具体的な例を以下に記載する.

RX パス

- 簡易的なデータフロー:

- mii_rx_0 → 外部ロジック

サブシステムの mii_rx_0 ポートからデータが外部ロジックや上位層に直接渡される。

- mii_rx_0 → 外部ロジック

- FIFO を使用する場合:

- mii_rx_0 → FIFO → 外部ロジックまたは上位層

mii_rx_0 と外部ロジックの間に FIFO を挿入し、クロックドメインの非同期性を吸収します。 - この場合、rx_clk_out_0 が FIFO の書き込みクロック、外部ロジックのクロック が FIFO の読み出しクロックになります。

- mii_rx_0 → FIFO → 外部ロジックまたは上位層

TX パス

- 簡易的なデータフロー:

- 外部ロジック → mii_tx_0

外部ロジックや上位層からのデータが直接 mii_tx_0 に入力される。

- 外部ロジック → mii_tx_0

- FIFO を使用する場合:

- 外部ロジック → FIFO → mii_tx_0

外部ロジック と mii_tx_0 の間に FIFO を挿入し、クロックドメインの非同期性を吸収します。 - この場合、外部ロジックのクロック が FIFO の書き込みクロック、tx_clk_out_0 が FIFO の読み出しクロックになります。

- 外部ロジック → FIFO → mii_tx_0

TXOUTCLKSEL_IN_0* と RXOUTCLKSEL_IN_0* に関して

これらに関しては,”7 シリーズ FPGA GTX/GTH トランシーバー ユーザー ガイド (UG476)” に説明がある.ここでは省略.

リセット

- sys_reset:GT,TX,RXコアを一括リセットする.

- gtwiz_reset_tx_datapath:TX側データパス(PMA+PCS)の行う.

- gtwiz_reset_rx_datapath:RX側データパス(PMA+PCS)の行う.

- tx_reset:TX回路用のリセット.アクティブHighでクロックが安定するまでHighにしておく必要あり.

- rx_reset:RX回路用のリセット.アクティブHighでクロックが安定するまでHighにしておく必要あり.

- user_tx_reset:GTのTX側のリセットが完了するとアサートされる.

PG210には”GT resetdone が Low または,クロックが不安定になったときにアサートされる”と記載されている.ここで,”GT resetdone” は 7 Series FPGAs GTX/GTH Transceivers User Guide (ug476) の Reset and Initialization を読むと,詳細がある.

ug476 中では,TXRESETDONE と記載されている.

(参考)TXRESETDONEがHighになると,GT トランシーバのリセットが完了し使用可能であることを表す. - user_rx_reset:GTのRX側のリセットが完了するとアサートされる.

このあたりの話を正確に理解しようとした場合には,GTトランシーバへの理解が必要になるので,GTX/GTHトランシーバやGTYトランシーバのユーザガイドも確認する必要があります.

統計カウンタ,その他

以下のポートは統計情報にアクセスするために利用される.pm_tickをアサートするとトリガーすることができるらしい.今回は省略する.

- pm_tick_*

- stat_tx_*

- stat_rx_*

- stat_rx_status:現在のリンク状況を出力

- user_reg0_*:User-defined signal from the AXI4-Lite Reg map user_reg0 register.

コメント