皆さん、突然ですが、「設計したIPを使い回したいけれど、元のバス幅は不要で、任意の範囲だけ使いたい」 という場面、よくありますよね?

Vivadoの仕様では、バス幅が異なる信号を接続すると、それぞれの下位ビットから自動的に接続される 仕様になっています。この仕様を理解したうえで使用すれば特に問題はありませんが、Critical Warningが表示される ため、気になることも多いでしょう。

そんな問題をスマートに解決してくれる便利なIPが XLSlice(スライス) です!

XLSlice IPの使い方

XLSliceを使うと、広いバスから特定のビット範囲だけを抜き出して使用 できるため、不要なビットをカットして設計をシンプルにできます。具体的な使い方を見ていきましょう。

1. XLSlice IPの追加

- VivadoのIPカタログ から「XLSlice」を検索し、デザインに追加します。

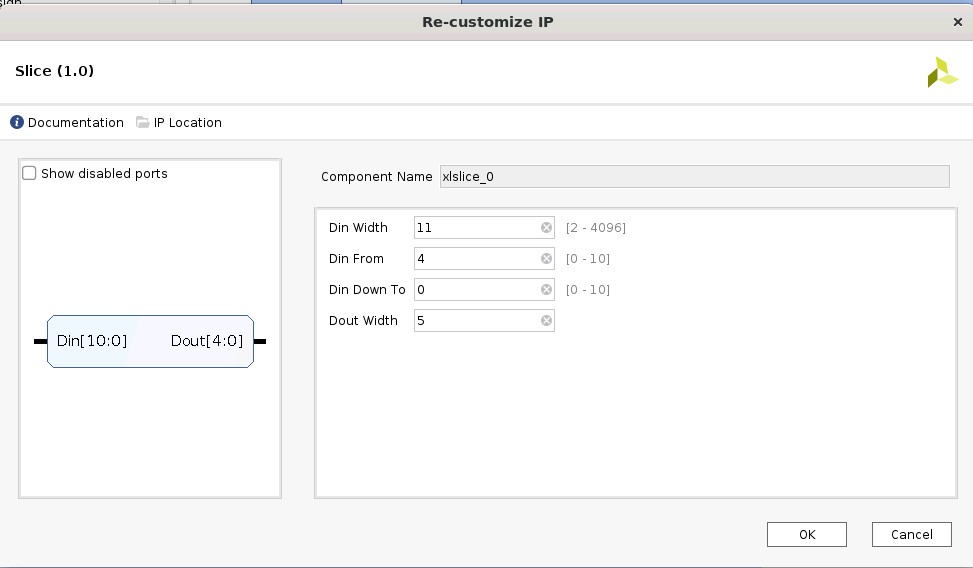

2. パラメータの設定

XLSliceには以下の3つの重要なパラメータがあります。

- Din Width :入力バスのビット幅(例:11ビット)

- Din From :抜き出す範囲の上位ビット(例:4)

- Din Down To :抜き出す範囲の下位ビット(例:0)

例えば、11ビットの入力バスから下位5ビット(ビット4~0)だけを使いたい 場合、次のように設定します。

- Din Width = 11

- Din From = 4

- Din Down To = 0

もし単一のビットだけを抜き出したい場合は、Din FromとDin Down Toを同じ値にする ことで可能です。

例えば、5ビット目(ビット5)だけを取り出す場合は、

- Din From = 5

- Din Down To = 5

と設定すればOKです。

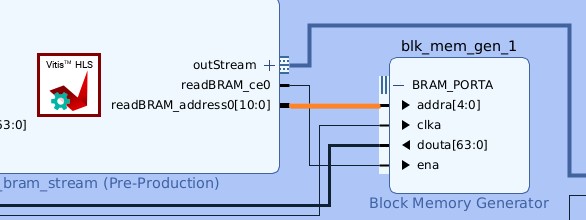

3. XLSliceの接続

設定が完了したら、抜き出したビットを必要なモジュールに接続するだけ!

これで、無駄なバスを使わずに、必要なビットだけを活用できます。

まとめ

XLSliceを活用すれば、不要なバス幅を意識せずに必要なビットだけを取り出してシンプルな設計が可能になります。

また、Critical Warningを回避できる ため、設計時のエラーや混乱も防げます。

Vivadoを使う際は、ぜひXLSliceを活用して、効率的な回路設計を実現しましょう!

詳細はこちらのプロダクトガイドをご覧ください。

PB042 – Slice v1.0 Product Brief (PB042) (v1.0)

コメント

参考になります